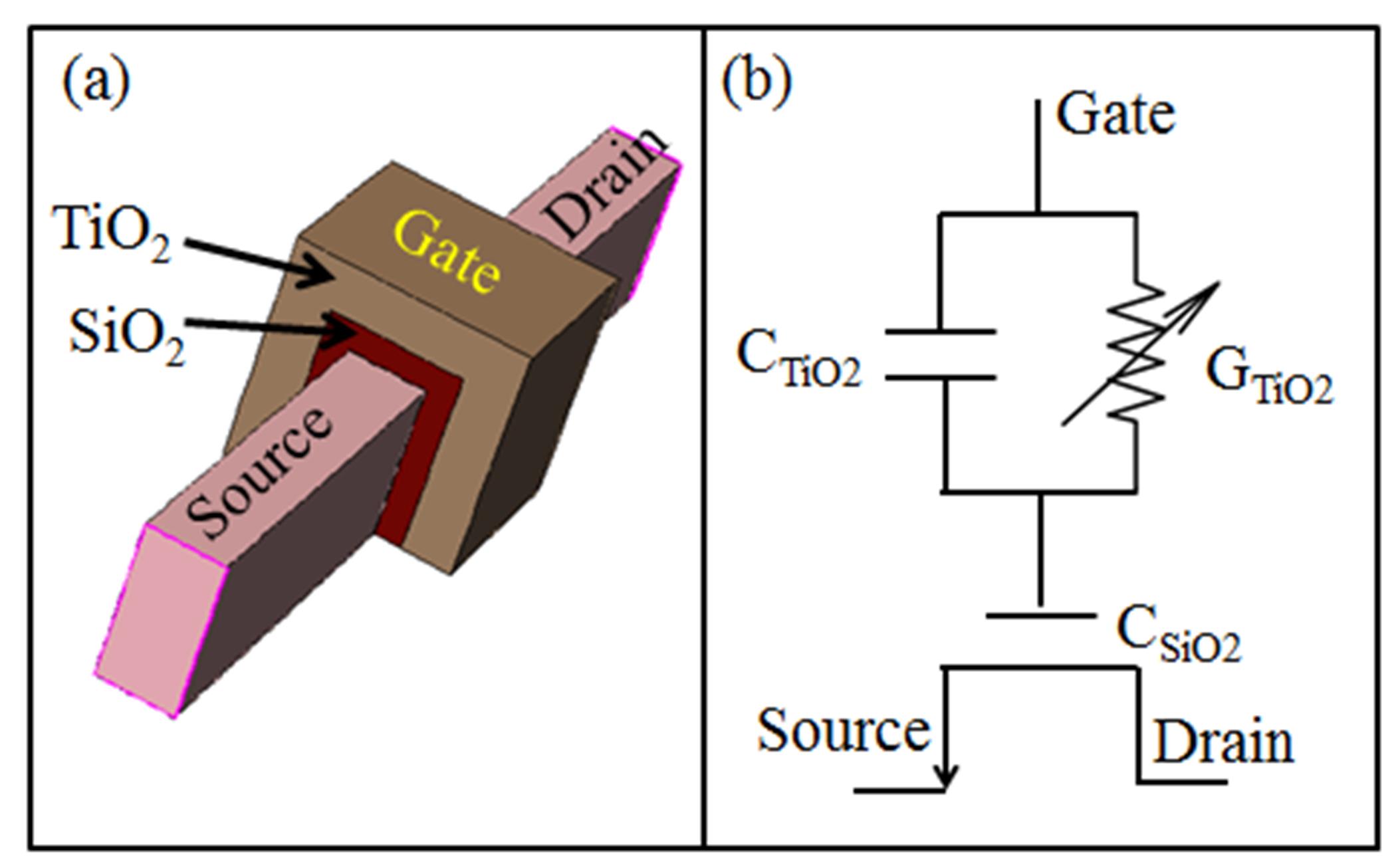

In this project we are building a unified memory device that shows both volatile and non-volatile operation in the same device. It operates by building the gate stack for a MOSFET as an RRAM. The conductance of the RRAM can be modulated by modulating the location of the oxygen vacancy layer in the gate. This (patented) concept grew out of the idea of modulating the conductance using two floating gates.

This research was/is funded by: NSF..

Selected Publications:

[1] Sarkar,B.;Ramanan, N.; Jayanti, S.; Spigna, N. D; Lee, B.; Franzon, P.; Misra, V.; “Dual floating gate unified MOSFET with simultaneous volatile and non-volatile operation”, IEEE Electron Device Letters, vol.35, no.1, pp.48-50, 2014.

[2] Sarkar, B.; Jayanti, S.; Spigna, N. D.; Lee, B.; Misra, V.; Franzon, P.; “Investigation of intermediate dielectric for dual floating gate MOSFET”, Non-Volatile Memory Technology Symposium (NVMTS), Minneapolis,USA,2013.

[3] Sarkar, B.; Lee, B.; Misra, V.; “Understanding the gradual reset in Pt/Al2O3/Ni RRAM for synaptic applications,” Semiconductor Science and Technology (accepted), 2015.

[4] Sarkar, B.; Lee. B.; Misra, V.; “Sarkar, B.; Lee. B.; Misra, V,” Device Research Conference (DRC), Ohio, USA, 2015.

[5] Sarkar, B.; Lee. B.; Misra, V.; "Implications of lower zero-field activation energy of dielectric in Al2O3/HfO2 bi-layer dielectric RRAM forming process," 226th ECS Meeting, Cancun, Mexico 2014.

[6] B. Sarkar, B. Lee, W.S. Pitts, V. Misra and P. Franzon, “A 1T-0C ZRAM using SiO2/non-filamentary RRAM in the transistor gate,” submitted for publication.

[7] B. Sarkar, W.S. Pitts, V. Misra and P. Franzon, “A hybrid RRAM-FT using non-filamentary RRAM,” accepted for 2016 16th Non-Volatile Memory Technology Symposium, (NVMTS 2016).

[8] N. DiSpigna, D. Schinke, S. Jayant, V. Misra, and P. Franzon, “A novel double floating-gate unified memory device,” in 20th IEEE/IFIP VLSI-SOC, pp. 53-58. 2012. [9]D. Schinke, N. DiSpigna, M. Shiveshwarkar, and P. Franzon, “Computing With Novel Floating Gate Devices”, in IEEE Computer, Vol. 44, No. 2, 2011, pp. 29-36.

[9] D. Schinke, S. Priyadarshi, W.S. Pitts, N.H. DiSpigna, P.D. Franzon, “SPICE-compatible Physical Model of Nanocrystal Floating Gate Devices for Circuit Simulation,” in IET Circuits, Devices and Systems, Vol. 5, No. 6, 2011, pp. 477-483.