Optimal codesign of chips and packages leads to higher system performance. The goals of this research area are to develop examples, and determine design methodology, for optimal chip-package codesign. Sub-projects include the following:

-

Spice2Ibis. Development of macromodels, and macromodeling tools for the support of the IBIS I/O CAD standard. For more information on this topic, please refer to www.ece.ncsu.edu/s2ibis

-

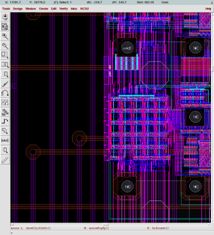

Optimal chip-package codesign. Mehtods and examples to improve performance or cost via chip-package codesign.

-

Other CAD toosl for chip-package codesign.

Selected Publications:

-

P. Franzon, Chip-package Codesign, in CRC Handbook on Design Automation

-

J.T. Schaffer, A. Glaser, S. Lipa, and P. Franzon, Chip Package Codesign of a Triple DES Processor,'' IEEE Trans. Advanced Packaging, 27(1), Feb. 2004, pp. 194-202

-

P. Mehrotra, P. Franzon, Optimal Chip Package Codesign for High Performance DSP, to appear in IEEE Trans. Advanced Packaging.

-

A.K. Varma, A.W. Glaser, and P.D. Franzon, CAD Flows for Chip-Package CoVerification, accepted by IEEE Trans. Advanced Packaging.

-

A. Varma, A. Glaser, S. Lipa , M.Steer, P. Franzon, The development of a macro-modeling tool to develop IBIS models, Proc. IEEE Electrical Performance of Electronic Packaging, Oct. 2003, pp. 177-280.